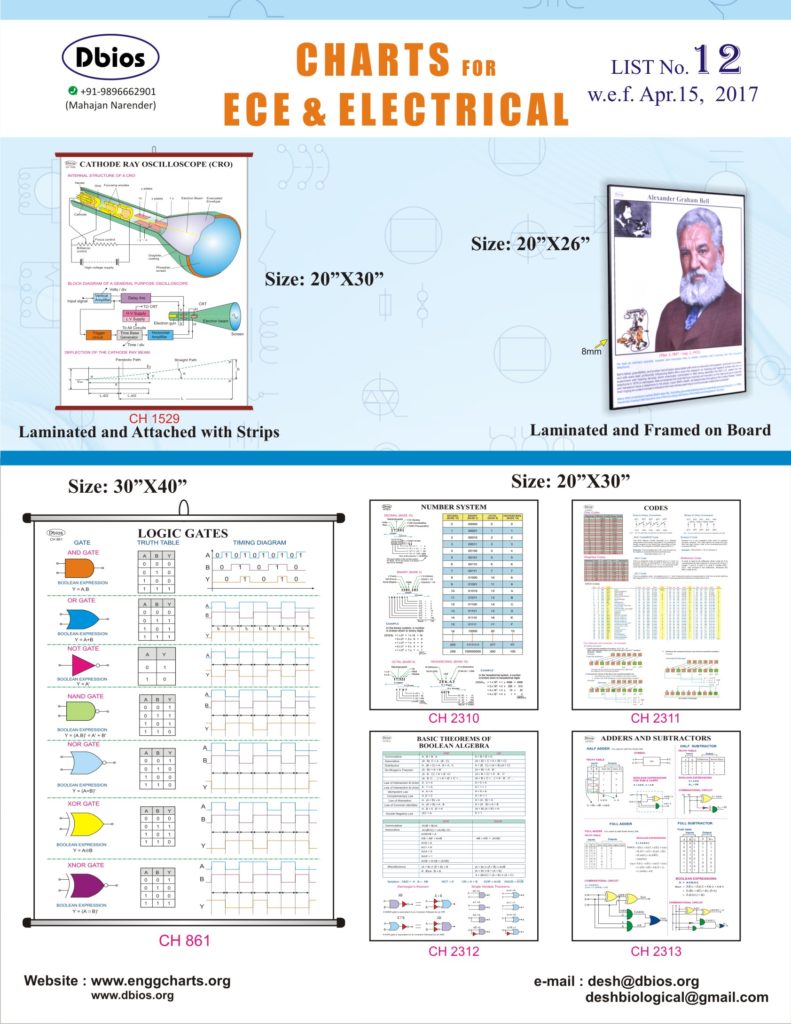

Dbios ECE -EEE / Electronics-Electrical Charts -Posters for Engineering , Polytechnics , Universities and Technical Institutes labs of AICTE Approved institutes in India. Dbios Civil charts are ready in three formats 50×75 cms Laminated and attached with plastic strips Or laminated and framed on wooden board Or Big sized charts 75x100cms Laminated and attached with plastic rollers. These can be customized as per your requirements of lab. Experimental Charts, Practical classes simplified, Basic Electrical Workshop, Electro – Magnetic Induction, DC Machines, Transformers, AC motor, Power Generation, Analog Devices, Network Analysis, Electronics Devices and circuit, Micro Processors, and controls,

Dbios Covered most of the Electronics Lab topics Dbios Can prepare customized charts also for your labs. For complete list of ECe-EEE charts visit Download section.

CH 2200 Safety Precautions in Electric Laboratory

CH 2201 Treatment Against Electric Shock

CH 2202 Electric Bell

CH 2203 Soldering Iron, Immersion Heater & Geyser

CH 2204 Electrical Accessories – I

CH 2205 Electrical Accessories – II

CH 2206 Procedure of Making & Joint

CH 2207 Types of Fuses

CH 2208 Basic Electrical Symbols

CH 2209 Light Bulb

CH 2210 Mercury Vapour Lamps

CH 2211 Fluorescent Tubes

CH 2212 Sodium Vapour Lamps

CH 2213 Wireman’s Toos – I

CH 2214 Wireman’s Toos – II.

CH 2215 Picture Tube

CH 2216 Watt Hour Meter

CH 2217 Cutaway of a Single Phase

CH 2218 Electrical Estimation and Costing

CH 2219 Stabilizers

CH 1541 8051 Architecture & Pin Layout

CH 1542 8051 Block Diagram

CH 1543 8051 Instruction Set

CH 1544 8051 SFR: Special Function Registers

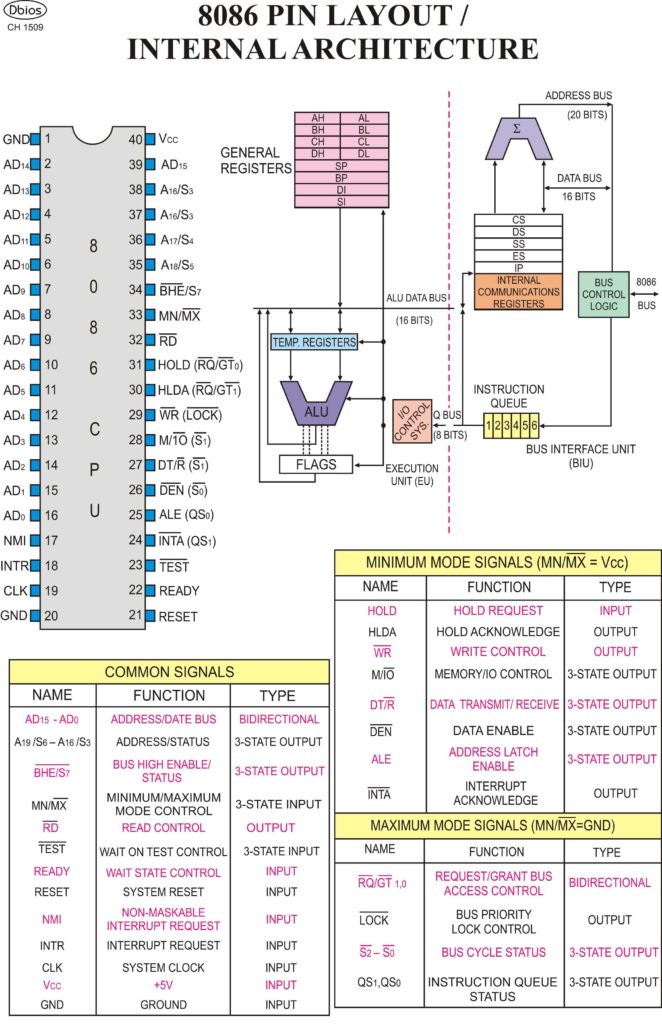

CH 1509 8086 Pin-layout & Architecture

CH 1545A 8086 Instruction Set

CH 1545B 8086 Instruction Set

CH 1510 8085 Block Diagram

CH 1511 8085 Pin Layout & Signal Representation

CH 1512 8085 Set Instruction

CH 1550 8085 Interrupts

CH 1513 8255a The Programmable Peripheral Interface

CH 1504 Radio Receivers

CH 1533 PLL(Phase Locked Loop)

CH 1538 Universal Shift Registers

CH 1539 ADC Techniques

CH 1540 DAC Techniques

CH 2314 Asynchronous Counters and Timing Diagram

CH 2315 Synchronous Counter and Timing Diagram

CH 2316 Internal Diagram of Memory (RAM/ROM)

VLSI & DSP

CH 1561 FABRICATION STEPS OF CMOS

CH 1562 STICK AND LAYOUT DIAGRAM OF LOGIC

CH 1563 High Level Design Flow: VHDL

CH 1564 TMS320C6713 ARCHITECTURE

CH 1565 RADIX 2 FFT ALGORITHM

CH 1566 DIGITAL IIR FILTER STRUCTURES

CH 1567 DIGITAL FIR FILTER STRUCTURES

CH 2378 Pulse Code Modulation (PCM)

CH 2379 A-law & μ-law Companding

CH 2380 Delta Modulation and Adaptive Delta

Modulation

CH 2381 Digital Carrier Line Encoding Techniques

CH 2382 FSK Detectors

CH 2383 Minimum Shift Keying (MSK) &Gaussian Minimum Shift Keying (GMSK)

CH 2317 Programmable Logic Arrays (PLA)

CH 2318 Programmable Array Logic (PAL)

CH 2319 Field Programmable Gate Array (FPGA)

CH 2320 Pseudo Random Sequen

CH 1546A Digital Modulation-I

CH 1546B Digital Modulation-II(Other Methods)

CH 1548 Sampling & Encoding Techniques

CH 1549 Multiple Access Techniques

(FDMA/CDMA/TDMA)

CH 2349 Types of Communication Transmission Systems

CH 2350 AM Transmission (Square Law/ Ring/ Balanced)

CH 2351 AM Receivers

CH 2352 AM Mixers

CH 2353 AM Detectors

CH 2354 FM Transmitters

CH 1505 FM Receivers

CH 2355 FM Stereo and 2-Way FM Radio

CH 1500 Wireless Communication Systems

CH 1501 Single Side Band Modulation

CH 2356 Single Side Band Reception

CH 2357 Pulse Amplitude Modulation (PAM)

CH 2358 Pulse Time/Pulse Width/ Pulse Position

CH 1502 Amplitude Modulation

CH 1503 Frequency Modulation